内存发展天梯图:解码计算性能提升的关键技术脉络

- 游戏动态

- 2025-10-28 07:44:43

- 27

解码计算性能提升的关键技术脉络

内存技术的发展,核心目标是解决CPU与内存之间的“速度鸿沟”,即CPU处理速度远快于内存读写速度的问题,其技术脉络遵循着“更快的速度、更大的容量、更低的功耗、更优的架构”这条主线。(来源:文章引言及核心观点)

第一阶段:技术萌芽与标准化(20世纪90年代前)

- 核心矛盾:早期计算机需要一种稳定、可读写的存储介质来替代速度慢且易失的磁鼓内存。

- 关键技术:

- 磁芯内存:在半导体内存普及前的主流技术,通过磁化小磁环的方向来存储0和1,它是不易失的,但制造工艺复杂、成本高昂、速度慢。(来源:对“磁芯内存”阶段的描述)

- DRAM的诞生与普及:英特尔1103 DRAM(1Kbit)的出现,标志着半导体内存时代的开启,它利用单个晶体管和电容存储数据,结构简单、成本低、容量易扩大,迅速取代磁芯内存,成为至今仍在使用的计算机主内存(内存条)的基础技术。(来源:对“DRAM动态随机存取存储器”阶段的描述)

第二阶段:接口提速与架构优化(20世纪90年代 - 21世纪初)

- 核心矛盾:如何让DRAM跟上CPU主频的飞速提升。

- 关键技术:

- SDR SDRAM:首次将内存工作频率与系统总线频率同步,在一个时钟周期内完成一次数据传输,结束了内存异步工作的时代,显著提升了数据传输效率。(来源:对“SDRAM同步动态随机存取存储器”阶段的描述)

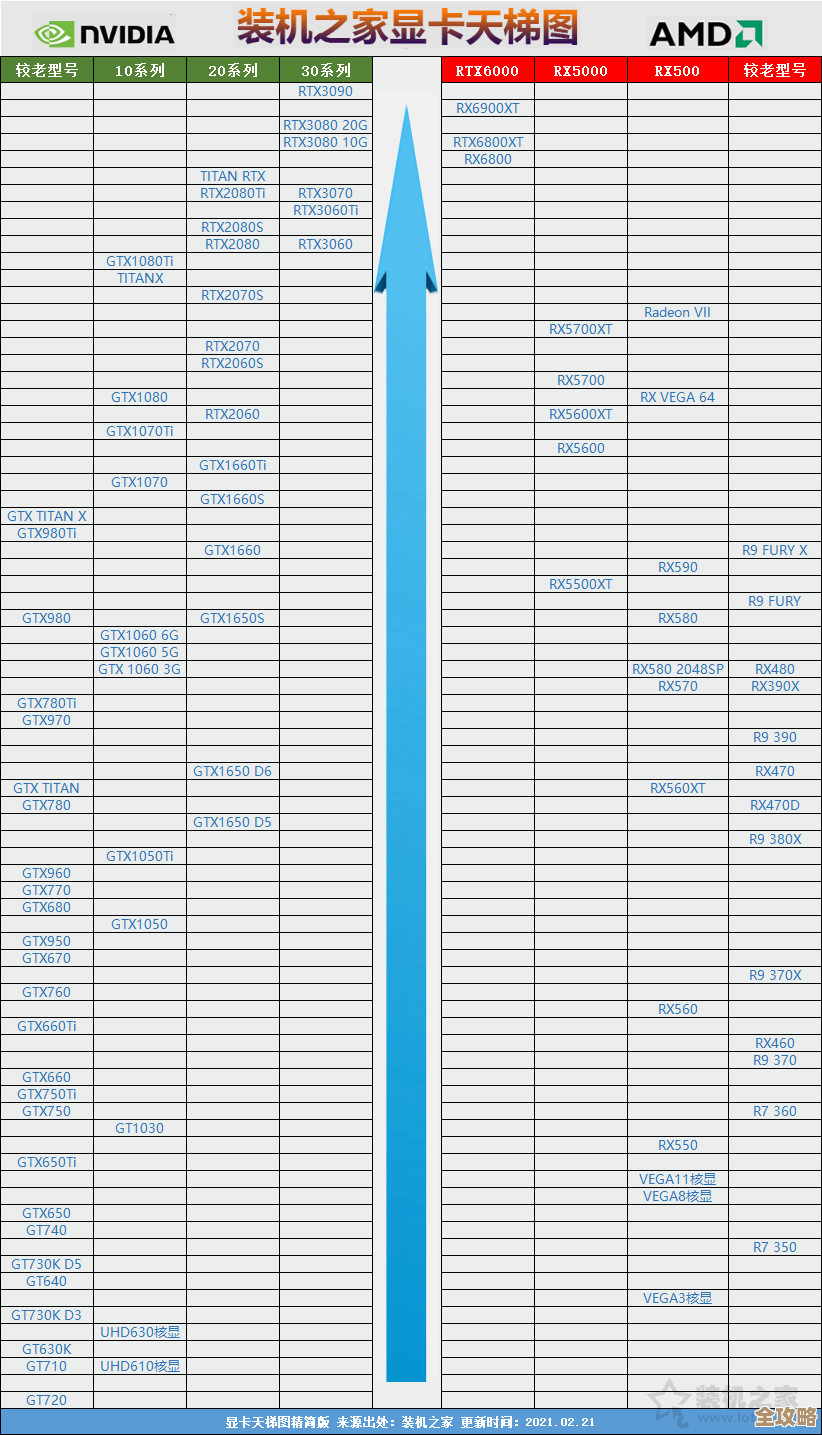

- DDR技术革命:这是内存发展的关键分水岭,DDR(双倍数据速率)技术在时钟脉冲的上升沿和下降沿各传输一次数据,在不提高核心频率的情况下将数据传输速率翻倍,后续的DDR2、DDR3、DDR4、DDR5每一代都在核心频率、预取位数、电压和带宽上进行了大幅优化,构成了清晰的内存性能“天梯”。(来源:对“DDR双倍数据速率”阶段的详细描述)

第三阶段:并行通道与专用化发展(21世纪初至今)

- 核心矛盾:单一内存通道的带宽成为瓶颈,以及满足不同计算场景的特定需求。

- 关键技术:

- 多通道技术:通过同时使用两条或更多条内存通道与内存控制器通信,实现带宽的成倍增加(如双通道、四通道),是提升整体性能最直接有效的手段之一。(来源:对“多通道内存技术”的描述)

- 显卡专用内存(GDDR):为图形处理单元(GPU)的高带宽需求而设计,与DDR追求低延迟不同,GDDR更专注于极高的数据传输速率,通过更宽的总线和更高的频率满足图形渲染和并行计算的需要,其发展路径同样经历了从GDDR到GDDR6X等的迭代。(来源:对“GDDR显卡专用内存”阶段的描述)

第四阶段:3D堆叠与近存计算(当前及未来方向)

- 核心矛盾:在物理定律限制下,传统2D平面缩放逼近极限,“内存墙”问题日益严峻。

- 关键技术:

- HBM:高带宽内存的代表,它通过3D堆叠技术将多个DRAM芯片堆叠在一起,并通过硅通孔(TSV)进行垂直互联,实现了超高的带宽、更小的占用面积和更低的功耗,主要用于高性能计算、AI加速等领域。(来源:对“HBM高带宽内存”阶段的描述)

- CXL:一种新兴的高速互连协议,它允许CPU、GPU、内存等设备高效共享内存资源,实现内存池化,有望打破每个设备拥有独立内存的传统架构,是解决数据中心资源利用率和性能瓶颈的未来关键技术。(来源:对“CXL”技术的描述)

- LPDDR:面向移动设备的低功耗内存,它在提供足够性能的同时,极致追求低功耗和小尺寸,是智能手机、平板电脑等设备的首选。(来源:对“LPDDR”技术的提及)

总结脉络:内存技术的发展从天梯图上看,是一条从“解决有无”(DRAM替代磁芯)到“提升速率”(DDR迭代),再到“增加并行度”(多通道、GDDR),最终走向“立体堆叠与架构革新”(HBM、CXL)的清晰路径,始终围绕着打破“内存墙”、释放计算潜力这一核心目标。(来源:文章各阶段总结及核心观点)

本文由疏鸥于2025-10-28发表在笙亿网络策划,如有疑问,请联系我们。

本文链接:http://www.haoid.cn/yxdt/49476.html