深入解析硬件加速核心机制:驱动现代计算效率飞跃的引擎

- 游戏动态

- 2025-10-15 19:32:27

- 14

哎,说到硬件加速…这玩意儿现在真是无处不在,但又好像隔着一层雾,很多人觉得它神秘,其实说白了,它就是个“偷懒”高手——让专门的硬件去干它最擅长的事,别让CPU那个万金油啥都掺和,想想啊,CPU就像个全能管家,能记账、能修水管、还能偶尔炒个菜,但每样都做…也就那样,不精啊。😅

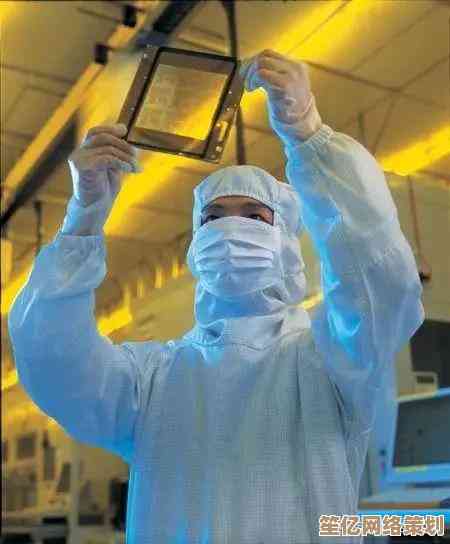

记得我第一次拆显卡的时候,看着那些密密麻麻的晶体管,心里嘀咕:这哪是显卡,分明是个小社会嘛…各司其职,GPU天生就是为并行计算生的,几千个小核心一起干活,你让CPU去处理图像像素?它得一个一个算…等到猴年马月,但GPU呢?唰一下,一片像素同时处理,这种“人海战术”在特定任务里简直是降维打击。

可硬件加速的核心机制,远不止GPU,比如TPU,谷歌专门为神经网络推理设计的,它连乘加运算的电路都是硬连线…几乎没调度开销,这就像…你修了条专用高铁,从A到B直达,中间不停站,而CPU得换乘公交、地铁,绕来绕去,但问题也在这儿——专用意味着僵化,TPU跑神经网络快得飞起,你让它解个压缩?它可能直接懵了。🤔

还有更细的…比如最近我在看一些AI芯片的论文,里面提到“近似计算”机制,这想法挺反直觉的:有些应用不需要100%精确,比如图像渲染里某些阴影计算,少算几位小数…人眼根本看不出来,硬件就在电路层做了取舍,用更少的晶体管、更低的功耗,换速度,这有点像…你煮汤时没必要用温度计精确到小数点后两位,大概沸腾就行,但这种“差不多”哲学,在传统CPU设计里简直是大逆不道。

再说说内存层次…硬件加速器往往自带高速缓存,或者用HBM堆在芯片旁边,为什么?因为数据搬运太耗电了!有时候计算只要1纳秒,等数据从内存跑来却要10纳秒…这就像你炒菜时火开得再旺,切菜慢吞吞,整体还是快不了,所以现在好多芯片设计,都在死磕怎么让数据离计算单元更近…甚至直接在内存里算(存内计算),这思路…真有点打破常规。

不过硬件加速也不是银弹,我遇到过一些项目,盲目上FPGA,结果算法迭代太快,硬件设计跟不上…最后反而拖慢进度,还有驱动兼容性…哎,说多都是泪,有一次调一个边缘设备,驱动版本差一点,整个加速功能直接趴窝,那时候真想砸了那板子…💢

其实想想,硬件加速的发展,很像社会分工的缩影,早期大家都种地,后来有了裁缝、铁匠…效率上去了,但依赖也强了,现在计算任务越来越复杂,CPU+GPU+TPU+各种IP核…得像指挥交响乐团一样协调它们,哪个环节掉链子,整体性能就崩了。

哦对了,还有软硬协同…这词听起来高大上,说白了就是硬件得提前知道软件要干啥,比如苹果的M系列芯片,为什么视频剪辑那么流畅?因为它从指令集层面就优化了视频编解码…软件和硬件简直像一对老夫妻,默契到不用说话,但这种深度定制,又带来了生态封闭的问题…真是矛盾。

回过头看,硬件加速的核心机制,其实是在通用和专用之间找平衡…在确定性和灵活性之间摇摆,未来会不会有更“通用”的加速器?或者…所有硬件都变成可重构的?不知道,但这种不确定性,反而让搞技术的人有点兴奋,就像拆解旧显卡时,我总感觉…里面藏着的不仅是电路,还有无数种未来的可能性。🚀

吧,硬件加速不是什么魔法,它只是人类偷懒智慧的延伸…让合适的工具做合适的事,但越是深入,越觉得这领域像片深海,每个浪头下面都藏着细节和陷阱,或许…这就是它的魅力?

本文由疏鸥于2025-10-15发表在笙亿网络策划,如有疑问,请联系我们。

本文链接:http://www.haoid.cn/yxdt/27197.html

![[epic下载]探索史诗级游戏世界,轻松下载尽享指尖乐趣!](http://www.haoid.cn/zb_users/upload/2025/12/20251204065519176480251916999.jpg)