手机芯片天梯图解析:从设计到制造的完整工艺探秘

- 游戏动态

- 2025-11-07 04:56:52

- 4

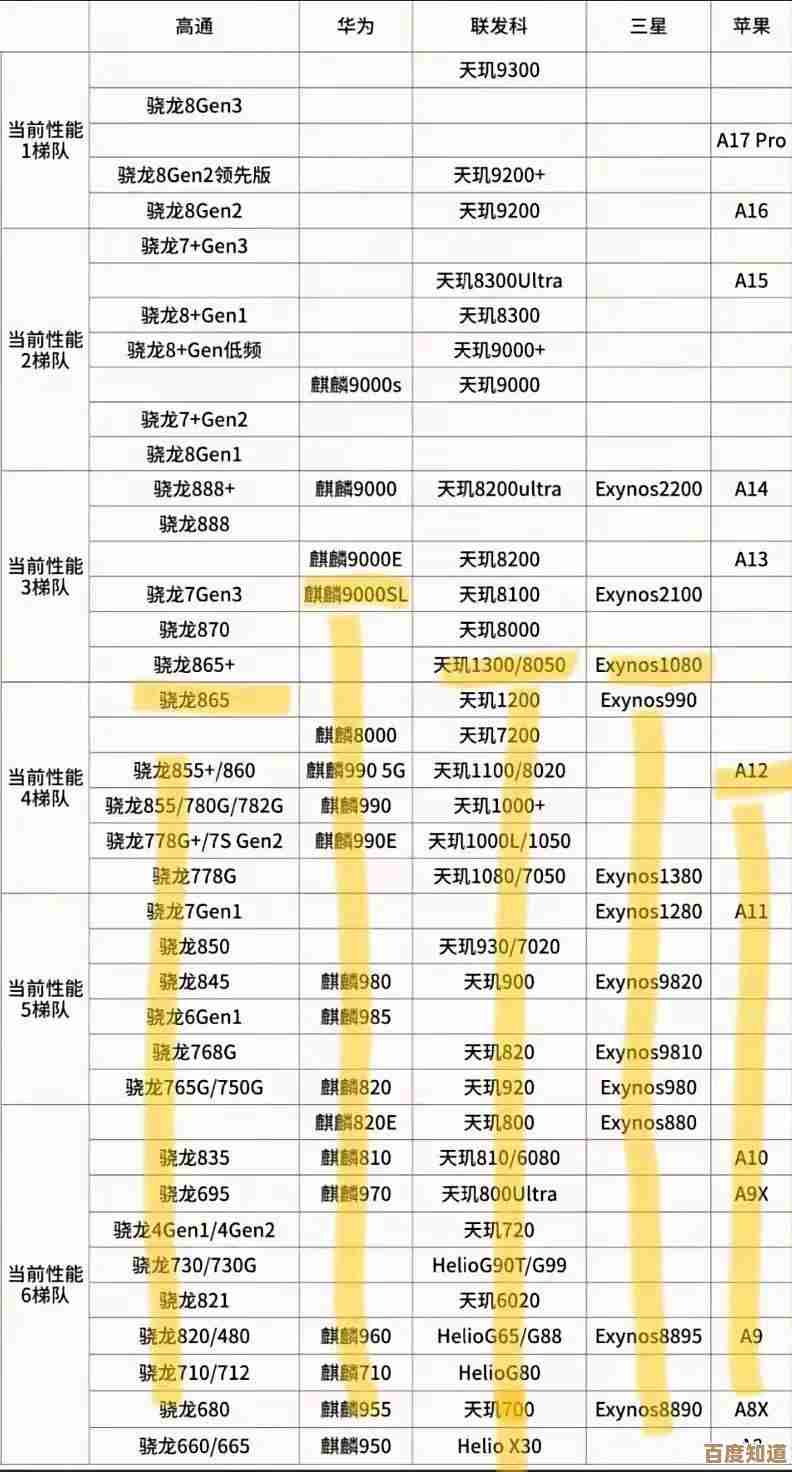

当我们谈论手机性能时,最常听到的就是“芯片”,而“手机芯片天梯图”则像一张武功排行榜,直观地告诉我们不同芯片的性能高低,但这张图背后的故事,远比排名本身要复杂和精彩,它实际上是一部从精妙设计到极限制造的科技史诗,要真正看懂天梯图,我们需要了解一颗芯片是如何从工程师的构思,最终变成我们手中手机里的“大脑”的。

第一步:精妙绝伦的蓝图设计——架构与IP核

芯片的旅程始于设计阶段,这就像建筑师绘制摩天大楼的蓝图,这里有几个关键角色,它们直接决定了芯片在“天梯图”上的起点。

最核心的“指令集架构”,你可以把它理解为芯片世界的“语言体系”或“宪法”,全球主流的两种架构是ARM和RISC-V,根据公开资料,比如来自ARM公司官网和行业分析报告,绝大多数手机芯片都采用ARM架构,ARM公司自己不生产芯片,而是提供这套基础设计规则和核心“模板”,芯片设计公司如苹果、高通、联发科等,需要获得ARM的授权。

接下来是“IP核”的使用,IP核就像是建筑中的预制件,比如已经设计好的门窗、楼梯,芯片设计公司不必从头设计每一个微小部件,可以直接购买或使用现成的成熟模块,比如CPU核心、GPU图形处理单元、基带(负责通信)等,根据公开的科技媒体报道,高通和苹果在CPU核心的设计上走了不同的路:苹果通常获得ARM的“架构授权”,这意味着它可以基于ARM的指令集,从头开始深度定制自己的CPU核心(如苹果的A系列芯片中的“闪电”、“暴风”核心),这种自研核心往往能实现极致的性能,这也是其长期霸占天梯图顶端的关键,而其他一些厂商可能直接使用ARM公版设计好的CPU核心,再进行集成和优化,这样效率更高,但性能天花板可能受限于公版设计。

设计团队使用强大的电子设计自动化软件,将数十亿甚至上百亿个晶体管像搭积木一样,在虚拟的芯片图纸上精确排列、连接,并反复进行模拟测试,确保逻辑正确,这个阶段的目标是打造出一个尽可能高效、强大的“灵魂蓝图”。

第二步:登峰造极的物理制造——纳米世界的雕刻

设计好的蓝图(称为GDSII文件)接下来要被送往芯片制造厂,也就是我们常说的“晶圆代工厂”,如台积电、三星等,这是将虚拟蓝图变为物理实体的魔法过程,其核心在于“制程工艺”,也就是我们常听到的“5纳米”、“4纳米”、“3纳米”。

这个“纳米”数,通俗地说,可以理解为芯片上晶体管之间连线的宽度,数字越小,意味着在同样大小的芯片面积上,能塞进的晶体管数量就越多,晶体管之间的信号传输距离就越短,根据台积电和三星的技术发布会信息,更先进的制程能带来更高的运算效率(性能更强)和更低的功耗(更省电),这就是为什么每一代新制程的出现,往往能催生出新一代的“旗舰芯片”,并迅速在天梯图上占据高位。

制造过程极其复杂,是在纯净度极高的硅晶圆上进行的,它涉及光刻、刻蚀、离子注入、薄膜沉积等数百道精密工序,以最核心的光刻为例,它就像用光作为刻刀,通过掩膜版将电路图案“投影”到涂有光刻胶的晶圆上,精度要求之高,相当于在一根头发丝的横截面上盖起一座摩天大楼,整个制造过程需要在无尘等级远超医院手术室的环境下进行,任何微小的尘埃都可能导致芯片报废。

第三步:封装测试与最终排名——天梯图的诞生

制造完成的晶圆上的芯片还只是一个个小方块,需要被切割下来,封装成我们看到的黑色小块,封装是为芯片加上保护外壳和连接外部的引脚,同时也要解决散热问题,之后,还要进行严格的测试,筛选出合格的产品。

当芯片被装入手机,科技媒体和评测机构会通过一系列标准化的性能测试(如Geekbench、GFXBench等),从CPU计算能力、GPU图形处理能力、AI性能、能效比等多个维度对其进行打分,这些海量的测试数据经过汇总、分析和对比,最终被整理成直观的排名图表——这就是我们看到的“手机芯片天梯图”。

天梯图上的每一次排名变化,不仅仅是数字的游戏,它背后凝聚着芯片设计公司架构师的智慧结晶,依赖于芯片制造厂在纳米尺度上鬼斧神工般的技艺,是设计、材料、工艺、封装测试整个产业链协同创新的最终体现,看懂了这个过程,我们再审视天梯图时,看到的就不再是冰冷的排名,而是一场人类智慧挑战物理极限的精彩竞赛。

本文由完芳荃于2025-11-07发表在笙亿网络策划,如有疑问,请联系我们。

本文链接:http://www.haoid.cn/yxdt/59582.html