揭秘新一代CPU架构:计算机性能飞跃的关键技术解析

- 问答

- 2025-11-11 20:53:19

- 3

(根据近期半导体行业分析报告及多家科技媒体对英特尔、AMD、ARM等公司新发布产品的技术解读综合整理)

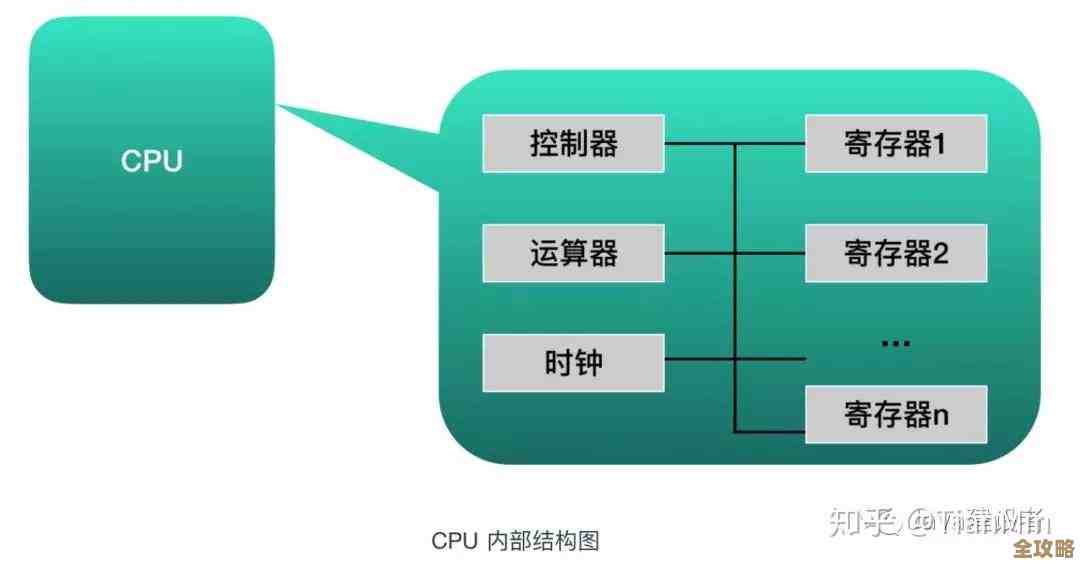

计算机的核心,也就是中央处理器(CPU),其架构的革新一直是推动整个信息时代前进的隐形引擎,当我们惊叹于手机运行速度更快、电脑游戏画面更逼真、数据中心处理海量数据的能力时,背后往往是CPU架构的升级在发挥作用,新一代的CPU架构究竟是如何实现性能的飞跃的呢?它并非依靠单一的“神奇”技术,而是一系列设计理念和工程技术协同进化的结果。

一个根本性的转变是从一味追求高时钟频率转向追求“更聪明”的执行效率,早些年,CPU性能提升很大程度上靠的是提高时钟频率,也就是让CPU的“心跳”更快,但这条路很快就遇到了瓶颈,过高的频率导致芯片发热巨大,能效比急剧下降,设计师们的思路变了,他们开始思考:如何在同一个时钟周期内让CPU完成更多的工作?这就引出了“更宽”和“更智能”的设计。

“更宽”可以理解为给CPU的内部处理通道进行“扩容”,想象一下CPU执行指令是一条流水线,传统的设计可能每次只拿取、解码、执行几条指令,而新一代架构,比如AMD的Zen系列和苹果的M系列芯片,大幅增加了这些环节的并行处理能力,它们可以同时拿取、解码更多的指令,并且拥有更多的执行单元(负责计算和处理的硬件模块),这就好比将一条乡间小路扩建为多车道高速公路,单位时间内能通过的车辆(指令)自然大大增加。

“更智能”则体现在CPU对指令执行顺序的优化上,程序中的指令并非总是可以一条接一条顺序执行的,有时一条指令需要等待前一条指令的结果,如果傻等,就会造成流水线的“堵车”,新一代架构采用了更先进的分支预测和乱序执行技术,分支预测就像是CPU有一个“预言家”,它能提前猜测程序接下来最可能走哪条路,并提前把指令准备好,大大减少了因“猜错”而浪费的时间,乱序执行则像一个高效的调度员,当发现某些指令不依赖于前面指令的结果时,它会重新排列指令的执行顺序,让那些能立刻执行的指令先“上车”,尽可能让所有的执行单元都忙碌起来,避免资源闲置,这些技术极大地提升了CPU的实际工作效率。

芯片设计范式从传统的“单一大核心”转向了“模块化”和“异构计算”,以前,提升性能可能意味着把所有晶体管都堆砌成一个巨大而复杂的核心,但现在,更流行的方式是采用模块化设计,AMD的Chiplet(小芯片)技术将CPU的不同核心组、输入输出控制器等部分,分别制成独立的小芯片,然后通过高速互联技术将它们封装在一起,这样做的好处很多:可以更灵活地组合配置,降低设计和制造成本,并且更容易针对不同市场推出不同规格的产品,这被行业分析机构视为提升性能和能效的关键路径之一。

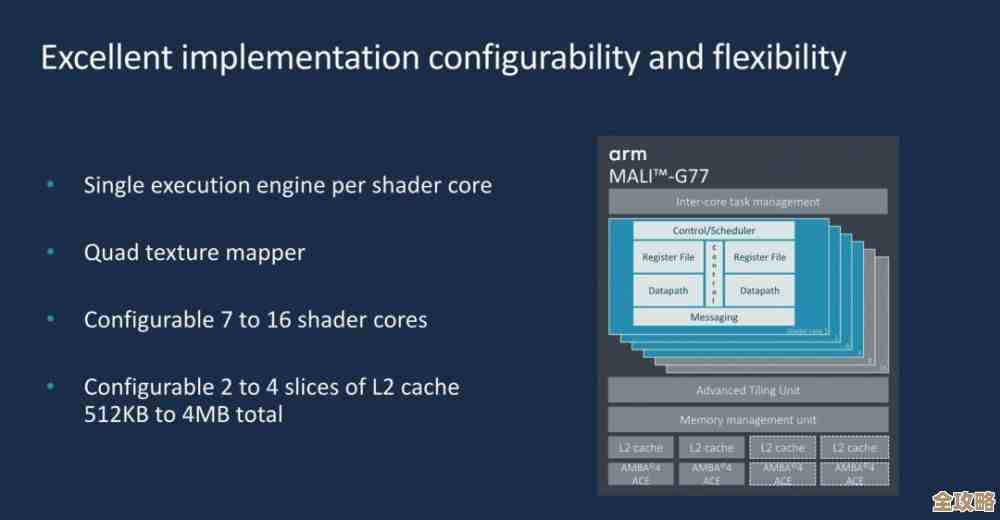

“异构计算”的理念则更进一步,它强调“让专业的部件处理专业的任务”,新一代CPU架构不再仅仅包含通用的计算核心,而是将整个处理器视为一个“计算系统”,在这个系统里,除了负责通用计算的高性能核心和能效核心(如英特尔的大小核架构)外,还紧密集成了专门用于图形处理的GPU、用于人工智能计算的NPU、负责图像处理的ISP等,这种设计使得特定的任务可以被调度到最擅长的硬件单元上去执行,整体能效和性能都得到优化,尤其是在AI应用爆发的今天,专用的AI引擎(NPU)能够以远高于通用CPU的效率和速度处理机器学习任务,这已经成为新一代CPU(特别是移动和客户端处理器)不可或缺的特性。

内存子系统和新一代制造工艺的进步是支撑上述所有创新的基础,CPU处理数据的速度再快,如果无法及时从内存中获取数据,也会陷入“无米下锅”的窘境,新一代架构普遍支持更快的内存标准(如DDR5、LPDDR5X),并加大各级缓存(Cache)的容量和优化其结构,缓存是CPU内部的高速数据仓库,更大的缓存意味着CPU有更高概率在“家门口”找到所需数据,减少等待从较慢的主内存中取数据的时间,这对提升实际应用性能至关重要。

更先进的半导体制造工艺(如台积电的3nm、5nm工艺)使得在同样大小的芯片面积内可以集成更多的晶体管,并带来更低的功耗,这不仅为增加CPU核心数量、扩大缓存提供了物理基础,也直接提升了能效比,让高性能计算在便携设备上成为可能。

新一代CPU架构的性能飞跃,是宽度扩展、智能调度、模块化异构集成、以及内存与工艺协同升级等多方面技术共同作用的结果,其核心目标不再是单纯追求峰值算力,而是在复杂的实际应用场景中,实现更高效、更智能、更均衡的性能与功耗表现,从而为从个人计算到云端数据中心的各类应用提供更强大的动力。

本文由芮以莲于2025-11-11发表在笙亿网络策划,如有疑问,请联系我们。

本文链接:http://www.haoid.cn/wenda/61672.html