探索芯片工艺天梯图:解码半导体制造的核心进展与创新路径

- 问答

- 2025-11-14 11:58:35

- 2

在谈论现代科技时,我们常常听到“5纳米芯片”、“3纳米工艺”这样的词汇,它们仿佛成了衡量手机或电脑性能高低的标尺,这背后所指的,正是半导体制造业的核心——芯片工艺制程,这张无形的“工艺天梯图”,清晰地勾勒出了人类在微观世界里不断攀登技术高峰的足迹,要理解这场静默却激烈的竞赛,我们需要解码它的核心进展与创新路径。

要理解工艺的进步,首先要明白一个关键概念:我们常说的“7纳米”、“5纳米”等数字,在今天已经不能简单地理解为晶体管内部某个具体栅极的实际物理宽度了,它更多是一个代表同一代技术整体水平的“工艺节点”名称,这个数字越小,意味着在同样大小的芯片面积上,能塞进越多的晶体管,芯片的性能就越强,或者功耗越低,攀登这座天梯的根本动力,就是让晶体管尽可能微小化、密集化。

这场攀登始于数十年前,遵循着所谓的“摩尔定律”——预言芯片上可容纳的晶体管数量每隔一段时间便会翻一番,最初的路径相对“笔直”,主要通过改进光刻技术来实现,光刻如同用光在硅片上“雕刻”电路,光源从早期的汞灯发展到深紫外光,让雕刻的线条越来越细,在这个过程中,传统的“平面晶体管”逐渐走到了物理极限,当工艺来到20纳米附近时,晶体管的栅极几乎无法有效控制电流的通断,出现了严重的漏电问题,就像关不紧的水龙头,导致芯片功耗和发热激增。

这时,攀登路径出现了第一次重大的、革命性的拐点,英特尔在2011年率先引入了“三维鳍式场效晶体管”(FinFET)技术,这被普遍认为是半导体制造业的一个里程碑,来源自《半导体国际》的行业分析指出,FinFET的创新在于将原来平躺的晶体管栅极结构“立”了起来,形成一个像鱼鳍一样的三维结构,这样一来,栅极对电流通道的控制能力大大增强,有效解决了漏电难题,使得工艺能够继续向16/14纳米及更小节点迈进,这项技术成为了此后近十年高端芯片制造的主流方案。

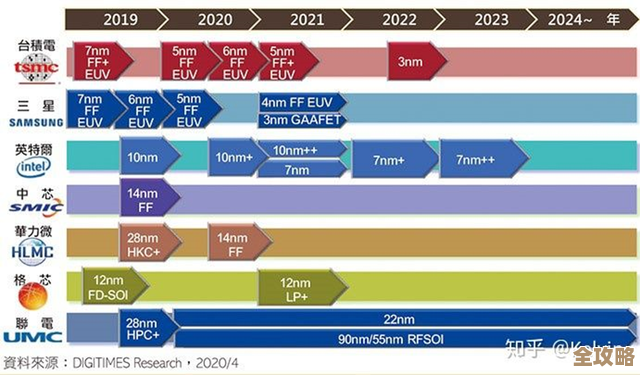

攀登不会停止,当工艺进入7纳米、5纳米节点后,即使是FinFET也再次面临挑战,晶体管尺寸小到原子级别,量子隧穿效应等更为复杂的物理现象开始显现,路径上出现了新的创新,极紫外光刻(EUV)技术成为了关键推手,相比之前的深紫外光,EUV的波长极短,能用更精确的“光刀”进行雕刻,大大简化了芯片制造的复杂工序,使制造更精细的图案成为可能,台积电和三星在5纳米及以下工艺中大规模应用EUV,标志着光刻技术进入了一个全新时代。

当前,我们正处在天梯图的又一个关键节点——3纳米和2纳米,FinFET在这里显得力不从心,行业开始探索更复杂的晶体管架构,一种被称为“全环绕栅极”(GAA)的技术被认为是未来的方向,根据IEEE(电气与电子工程师协会)发布的学术研究综述,GAA技术将电流通道用栅极材料从多个面包围起来,实现了比FinFET更彻底的控制,三星已在其3纳米工艺中率先采用了名为MBCFET的GAA变体技术,而台积电和英特尔也计划在2纳米时代引入类似的结构,这标志着晶体管结构从二维到三维,再到被栅极全方位环绕的又一次进化。

展望更遥远的未来,比如1纳米甚至更小的尺度,攀登路径将更加依赖基础材料的创新,来源自《自然》杂志的科研论文显示,科学家们正在研究诸如二维材料、碳纳米管等可能取代传统硅基通道的新材料,以及芯片三维堆叠等系统级创新,以继续推动计算能力的提升。

芯片工艺的天梯图,并非一条简单的线性赛道,而是一个充满智慧拐点的创新路径,它从追求尺寸缩小的“直路”,到引入FinFET的“弯道超车”,再到依靠EUV和GAA的“架桥铺路”,每一步都是对物理极限的挑战和对技术瓶颈的突破,这张不断延伸的天梯图,不仅解码了半导体制造的核心进展,更清晰地指向了未来计算世界的无限可能。

本文由符海莹于2025-11-14发表在笙亿网络策划,如有疑问,请联系我们。

本文链接:http://www.haoid.cn/wenda/62190.html